- In:

- Posted By: Capuano Edoardo

- Commenti: 0

Una tecnica di impilamento elettronico potrebbe aumentare esponenzialmente il numero di transistor sui chip, consentendo di realizzare hardware di intelligenza artificiale più efficienti

La richiesta di integrazione tridimensionale (3D) di componenti elettronici è in costante aumento. Nonostante le sostanziali sfide di elaborazione, la tecnica through-silicon-via (through-silicon-via / TSV) emerge come l'unico metodo praticabile per integrare componenti di dispositivi monocristallini in un formato 3D. Sebbene gli schemi di integrazione 3D monolitica (monolithic 3D / M3D) siano promettenti, la connessione perfetta di semiconduttori monocristallini senza wafer intermedi deve ancora essere dimostrata. Questa sfida nasce dalla difficoltà intrinseca di far crescere singoli cristalli su superfici amorfe o policristalline dopo il processo back-end-of-the-line a basse temperature per preservare i circuiti sottostanti. Di conseguenza, una soluzione pratica basata sulla crescita per M3D di cristalli singoli rimane sconosciuta.

L'industria elettronica si sta avvicinando al limite del numero di transistor che possono essere impacchettati sulla superficie di un chip per computer. Quindi, i produttori di chip stanno cercando di costruire piuttosto che di espandersi.

Invece di comprimere transistor sempre più piccoli su una singola superficie, l'industria punta a impilare più superfici di transistor ed elementi semiconduttori, un po' come trasformare una casa colonica in un grattacielo. Questi chip multistrato potrebbero gestire esponenzialmente più dati e svolgere molte più funzioni complesse rispetto all'elettronica odierna.

Un ostacolo significativo, tuttavia, è la piattaforma su cui vengono costruiti i chip. Oggi, ingombranti wafer di silicio fungono da impalcatura principale su cui vengono coltivati elementi semiconduttori monocristallini di alta qualità. Qualsiasi chip impilabile dovrebbe includere una “pavimentazione” di silicio spessa come parte di ogni strato, rallentando qualsiasi comunicazione tra strati semiconduttori funzionali.

Ora, gli ingegneri del MIT hanno trovato un modo per aggirare questo ostacolo, con un design di chip multistrato che non richiede alcun substrato di wafer di silicio e funziona a temperature sufficientemente basse da preservare i circuiti dello strato sottostante.

In uno studio pubblicato oggi sulla rivista Nature (1), il team riferisce di aver utilizzato il nuovo metodo per fabbricare un chip multistrato con strati alternati di materiale semiconduttore di alta qualità, fatti crescere direttamente uno sopra l'altro.

Il metodo consente agli ingegneri di costruire transistor ad alte prestazioni, elementi di memoria e logici su qualsiasi superficie cristallina casuale, non solo sull'ingombrante impalcatura cristallina dei wafer di silicio. Senza questi spessi substrati di silicio, più strati semiconduttori possono essere in contatto più diretto, portando a una migliore e più rapida comunicazione e calcolo tra gli strati, affermano i ricercatori.

Gli ingegneri immaginano che il metodo potrebbe essere utilizzato per costruire hardware di intelligenza artificiale, sotto forma di chip impilati per computer portatili o dispositivi indossabili, che sarebbero veloci e potenti come i supercomputer odierni e potrebbero archiviare enormi quantità di dati alla pari dei data center fisici.

«Questa svolta apre un potenziale enorme per l'industria dei semiconduttori, consentendo di impilare i chip senza le limitazioni tradizionali», afferma l'autore dello studio Jeehwan Kim (2), professore associato di ingegneria meccanica al MIT. «Ciò potrebbe portare a miglioramenti di ordini di grandezza nella potenza di calcolo per applicazioni in intelligenza artificiale, logica e memoria».

Tasche per semi

Nel 2023, il gruppo del professor Kim ha riferito di aver sviluppato un metodo (3) per far crescere materiali semiconduttori di alta qualità su superfici amorfe, simili alla topografia diversificata dei circuiti semiconduttori sui chip finiti. Il materiale che hanno coltivato era un tipo di materiale 2D noto come dicalcogenidi di metalli di transizione, o TMD, considerato un promettente successore del silicio per la fabbricazione di transistor più piccoli e ad alte prestazioni. Tali materiali 2D possono mantenere le loro proprietà semiconduttrici anche a scale piccole come un singolo atomo, mentre le prestazioni del silicio si degradano drasticamente.

Nel loro lavoro precedente, il team ha fatto crescere i TMD su wafer di silicio con rivestimenti amorfi, così come su TMD esistenti. Per incoraggiare gli atomi a disporsi in una forma monocristallina di alta qualità, piuttosto che in un disordine policristallino casuale, Kim e i suoi colleghi hanno prima ricoperto un wafer di silicio con una pellicola molto sottile, o “maschera” di biossido di silicio, che hanno modellato con piccole aperture o tasche. Hanno quindi fatto scorrere un gas di atomi sulla maschera e hanno scoperto che gli atomi si depositavano nelle tasche come “semi”. Le tasche confinavano i semi a crescere in modelli monocristallini regolari.

Ma all'epoca il metodo funzionava solo a circa 900 gradi Celsius.

«Bisogna far crescere questo materiale monocristallino sotto i 400 gradi Celsius, altrimenti il circuito sottostante viene completamente cotto e rovinato», dice Kim. «Quindi, il nostro compito era di fare una tecnica simile a temperature inferiori ai 400 gradi Celsius. Se fossimo riusciti a farlo, l'impatto sarebbe stato sostanziale».

Costruire

Nel loro nuovo lavoro, Kim e i suoi colleghi hanno cercato di mettere a punto il loro metodo per far crescere materiali 2D monocristallini a temperature sufficientemente basse da preservare qualsiasi circuito sottostante. Hanno trovato una soluzione sorprendentemente semplice nella metallurgia, la scienza e l'artigianato della produzione dei metalli. Quando i metallurgisti versano metallo fuso in uno stampo, il liquido lentamente “nuclea”, ovvero forma grani che crescono e si fondono in un cristallo con motivi regolari che si indurisce in forma solida. I metallurgisti hanno scoperto che questa nucleazione avviene più facilmente ai bordi di uno stampo in cui viene versato il metallo liquido.

«È noto che la nucleazione ai bordi richiede meno energia e calore», afferma Kim. «Quindi abbiamo preso in prestito questo concetto dalla metallurgia per utilizzarlo per l'hardware AI futuro».

Il team ha cercato di far crescere TMD monocristallini su un wafer di silicio che era già stato fabbricato con circuiti a transistor. Hanno prima ricoperto i circuiti con una maschera di biossido di silicio, proprio come nel loro lavoro precedente. Hanno poi depositato “semi” di TMD ai bordi di ciascuna tasca della maschera e hanno scoperto che questi semi di bordo crescevano in materiale monocristallino a temperature basse fino a 380 gradi Celsius, rispetto ai semi che iniziavano a crescere al centro, lontano dai bordi di ciascuna tasca, che richiedevano temperature più elevate per formare materiale monocristallino.

Facendo un ulteriore passo avanti, i ricercatori hanno utilizzato il nuovo metodo per fabbricare un chip multistrato con strati alternati di due diversi TMD: bisolfuro di molibdeno, un promettente materiale candidato per la fabbricazione di transistor di tipo n; e diseleniuro di tungsteno, un materiale che ha il potenziale per essere trasformato in transistor di tipo p. Sia i transistor di tipo p che quelli di tipo n sono i mattoni elettronici per eseguire qualsiasi operazione logica. Il team è stato in grado di far crescere entrambi i materiali in forma monocristallina, direttamente uno sopra l'altro, senza richiedere wafer di silicio intermedi. Kim afferma che il metodo raddoppierà efficacemente la densità degli elementi semiconduttori di un chip e, in particolare, del semiconduttore in ossido di metallo (CMOS), che è un mattone fondamentale di un moderno circuito logico.

Il dottor Jeehwan Kim racconta: «Un prodotto realizzato con la nostra tecnica non è solo un chip logico 3D, ma anche una memoria 3D e le loro combinazioni. Con il nostro metodo 3D monolitico basato sulla crescita, potresti far incrementare decine o centinaia di livelli di logica e memoria, uno sopra l'altro, e sarebbero in grado di comunicare molto bene».

«I chip 3D convenzionali sono stati fabbricati con wafer di silicio centrale, perforando i fori attraverso il wafer, un processo che limita il numero di strati impilati, la risoluzione dell'allineamento verticale e le rese», aggiunge il primo autore Kiseok Kim (4). «Il nostro metodo basato sulla crescita affronta tutti questi problemi contemporaneamente».

Per commercializzare ulteriormente il design del suo chip impilabile, Kim ha recentemente fondato una società, FS2 (Future Semiconductor 2D materials).

«Finora abbiamo mostrato un concetto in array di dispositivi su piccola scala», afferma. «Il passo successivo è quello di aumentare la scala per mostrare il funzionamento professionale dei chip AI».

I coautori del MIT dello studio includono il primo autore Ki Seok Kim, Seunghwan Seo, Doyoon Lee, Jung-El Ryu, Jekyung Kim, Jun Min Suh, June-chul Shin, Min-Kyu Song, Jin Feng, e Sangho Lee, insieme ai collaboratori di Samsung Advanced Institute of Technology, Sungkyunkwan University in South Korea, e l'University of Texas a Dallas. Questa ricerca è supportata, in parte, da Samsung Advanced Institute of Technology e l'U.S. Air Force Office of Scientific Research.

Riferimenti:

(1) Growth-based monolithic 3D integration of single-crystal 2D semiconductors

(2) Jeehwan Kim

(3) MIT engineers grow “perfect” atom-thin materials on industrial silicon wafers

(4) Kiseok Kim

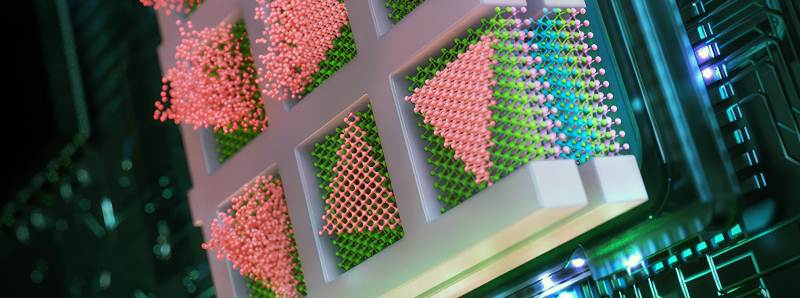

Descrizione foto: Gli ingegneri del MIT hanno sviluppato un metodo per impilare senza soluzione di continuità strati elettronici per creare chip per computer più veloci, più densi e più potenti. Il team deposita particelle semiconduttrici (in rosa) come triangoli all'interno di quadrati confinati, per creare elementi elettronici di alta qualità, direttamente sopra altri strati semiconduttori (mostrati in strati di viola, blu e verde). - Credit: Cube 3D Graphic.

Autore traduzione riassuntiva e adattamento linguistico: Edoardo Capuano / Articolo originale: MIT engineers grow “high-rise” 3D chips